LogiCORE™ IP核AXI通用异步收发器(UART)Lite核提供UART信号和高级微控制器总线体系结构(AMBA)AXI接口,还为异步串行数据发送提供控制器接口。这个LogiCORE™ IP核设计用于与AXI4 Lite协议接口。

功能

框图

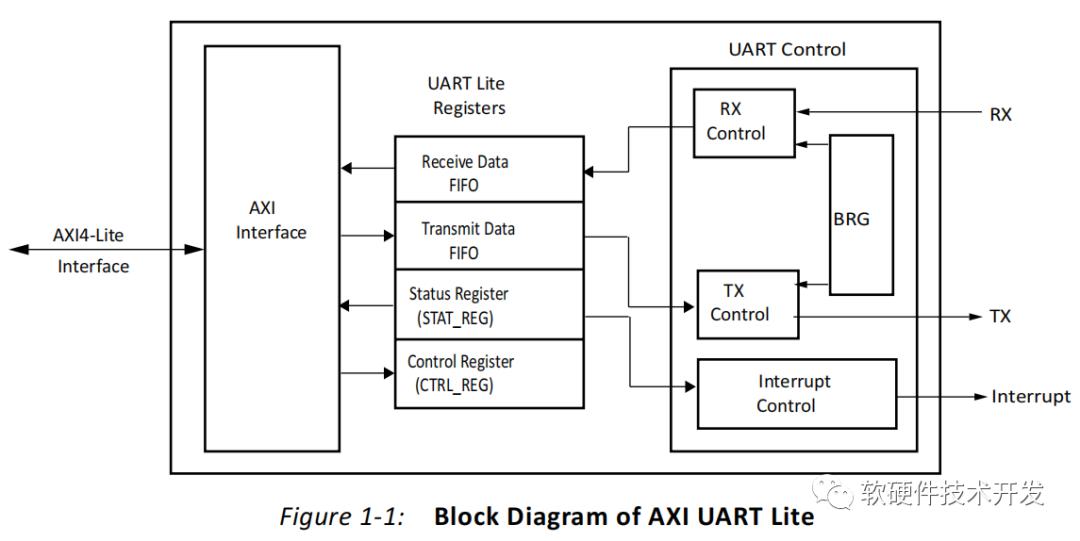

图 1 AXI UART Lite框图

图 1 AXI UART Lite框图• AXI接口:实现AXI4 Lite从接口,用于寄存器访问和数据发送。• UART Lite寄存器:包括内存映射寄存器(如图 1所示)。它由一个控制寄存器、一个状态寄存器和一对发送/接收FIFO,均为16bits深度。• UART控制:

Rx控制 - 根据生成的波特率对接收到的数据进行采样,并将其写入接收数据FIFO。

Tx控制 - 从发送数据FIFO读取数据,并将其发送到UART Tx接口。

BRG(波特率生成器)- 编程时生成各种波特率。

中断控制 - AXI UART Lite内核提供中断启用/禁用。如果中断被启用,当接收FIFO变为非空或发送FIFO变为空时,将生成上升沿敏感中断。

功能介绍

对通过AXI4 Lite接口接收的字符执行并行到串行转换,并对从外设的串行接口接收的字符执行串行到并行转换。

发送和接收8、7、6或5位数据,以及一个停止位和奇偶校验位。AXI UART Lite可以独立发送和接收。

当接收FIFO变为非空或发送FIFO变为空时,生成上升沿敏感中断。可以使用启用/禁用信号来开启。该设备包含一个波特率发生器和独立的16bits深度的发送和接收FIFO。

软硬件技术开发